Vol. 25 No. 8 Aug. 2003

# 32 通道声发射特征参数的实时提取

——现场可编程门阵列的设计

#### 夏展宏,刘时风

(清华大学 机械工程系,北京 100084)

摘 要:采用硬件描述语言 VHDL(very-high-speed integrated circuit hardware description language)设计出现场可编程门阵列(FPGA)芯片,实时提取 32 通道的声发射信号的两个特征参数(到达时间和声发射振铃计数),以实现声发射源定位以及强度评价。

关键词:声发射检验;声发射信号;现场可编程门阵列

中图分类号:TG115.28

文献标识码:A

文章编号:1000-6656(2003)08-0390-04

### ACQUISITION OF 32-CHANNEL ACOUSTIC EMISSION PARAMETERS: DESIGN OF FIELD PROGRAMMABLE GATE ARRAY

#### XIA Zhan-hong, LIU Shi-feng

(Department of Mechanical Engineering, Tsinghua University, Beijing 100084, China)

Abstract: An FPGA(field programmable gate array) chip was developed with VHDL(very-high-speed integrated circuit hardware description language) for real-time picking-up of two acoustic emission parameters(arriving time & ring count) in 32-channel acoustic emission testing, which could be used to realize source location and intensity evaluation.

设计领域。

ASIC 的设计。

特征参数的实时提取。

Keywords: Acoustic emission testing; Acoustic emission signal; Field programmable gate array

FPGA<sup>[1,2]</sup>是一种可由用户根据所设计的数字系统要求,在现场自由配置和定义的高密度专用数字集成电路。FPGA 将现代 VLSI(超大规模集成电路)逻辑集成的优点和可编程器件设计灵活、上市快速的长处相结合,使设计者在 FPGA 开发系统软件的支持下,现场直接根据系统要求定义和修改逻辑功能,短期内即可完成大规模复杂数字系统的设计。基于上述优点,FPGA 已广泛用于现代电子系统,成为系统设计及 ASIC(专用集成电路)验证的一种重要手段。

VHDL<sup>[3]</sup>语言最初是在 20 世纪 80 年代后期由 美国国防部开发的,1987 年 12 月由 IEEE 标准化 (定为 IEEE 1076—1987 标准,1993 年进一步修订, 定为 ANSI/IEEE 1076—1993 标准),成为 IEEE 的 工业标准,VHDL 语言已经广泛应用于数字系统

1 用 VHDL 进行 FPGA 设计

#### 1.1 FPGA 芯片的输入输出信号

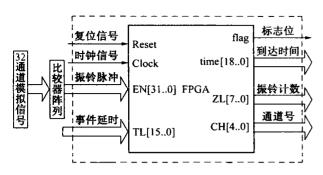

根据声发射检测的实际情况以及预期所要实现的功能,所设计的 FPGA 芯片输入输出信号见图 1。

与系统硬件设计的传统方法相比,VHDL语言的优点是① 功能强大,可进行系统级的硬件描述。

② 与具体器件和工艺无关,设计者在用 VHDL 进行系统设计时不必十分熟悉器件的结构。③ 作为

一种 IEEE 的工业标准, VHDL 语言使设计成果便

于共享和复用。④ 具有很好的可移植性,用 VHDL 语言可以把综合到 FPGA 的设计很容易地转成

笔者将上述技术应用于声发射检测,用 VHDL 语言设计 FPGA 芯片,以实现 32 通道声发射信号

收稿日期:2002-06-17

基金项目:北京市自然科学基金资助项目(3011001)

图 1 FPGA 芯片的输入输出信号(虚线框内)

#### 1.1.1 输入信号

#### (1) 复位信号 Reset

该信号采用异步复位的方式,用于整个芯片的 复位,并建立初始状态。

#### (2) 时钟信号 Clock

该信号给整个芯片以同步方式工作提供时钟, 同时还为记录信号到达时间提供基准。

时钟频率的高低取决于声发射信号的频率、声发射源定位精度要求以及 FPGA 的最高工作速度,在满足 FPGA 工作速度的前提下,时钟频率越高,可记录声发射信号的频率也越高,记录到达时间的精度也越高(通常记录的最大误差为一个时钟周期),相应记录的位数(即计数器的位数)也越长。笔者初步设定时钟频率 f=30MHz。该频率可以满足32 通道的声发射信号频率(典型声发射信号为几百千赫)的要求。 FPGA 芯片记录的到达时间误差最大为一个时钟周期,因此产生的定位最大误差  $\delta$  为

$$\delta = \frac{v}{f} \tag{1}$$

式中 v——声速(在金属压力容器中,声速通常取 3 000m/s)

代人数据得  $\delta$ =0. 1mm,由此可见笔者设计的 FP-GA 芯片在记录到达时间方面具有很高精度,所产生的定位误差很小,与检测中其它因素引起的定位误差相比可忽略不计。

#### (3) 32 通道振铃脉冲信号 EN

EN 由声发射信号与比较器的比较电平相比较而产生,一旦声发射信号越过预先设定的参考门限,就产生振铃脉冲,对应的 EN 有效,在满足一定条件下,芯片将记录该振铃脉冲的到达时间、振铃计数和相应的通道号,同时输出标志位。

#### (4) 事件延时信号 TL

在声发射检测中,为了消除由于边界反射以及 频散产生的影响,引进了事件延时信号,事件延时的 取值与声发射信号的强弱、传播距离以及介质的厚度等因素有关<sup>[4]</sup>,TL 应能选择,并有一定范围。

笔者用 16 位数据宽度来表示事件延时值 TL, 由此得到 TL 的范围为 0~2. 2ms。

#### 1.1.2 输出信号

#### (1) 信号到达时间

该输出信号用于记录声发射信号的到达时间。 其数据宽度决定发射检测中两个声发射信号之间的 最大距离  $L_{\max}$ ,通常情况下  $L_{\max} \approx 50 \text{m}$ ,因此可根据 该值来确定数据宽度 N

$$L_{\text{max}} = v \frac{2^N}{f} \tag{2}$$

$$N = \log_2\left(L_{\text{max}} \frac{f}{v}\right) \tag{3}$$

代人数据得 N=18.9,因此取 N=19 即可满足上述要求。

#### (2) 通道号

该信号用于记录声发射信号所对应的通道号, 总数为32通道,因此可用5位数据宽度来实现。

#### (3) 振铃计数

该信号用于记录一个声发射信号所产生的振铃脉冲数。由于最终得到的数据将以 PCI 总线方式进行传送,因此总的输出数据宽度是 32 位,由此可得振铃计数的数据宽度为 8 位,从而得到记录的最大振铃数为 256,通常能满足声发射信号的要求。

#### (4) 标志位

高电平有效,用于表示 FPGA 已经记录到声发射信号特征参数,便于后续电路读取这些特征参数。

#### 1.2 用 VHDL 进行功能描述 [5]

VHDL语言具有 Top-Down(自顶而下)的设计特点,因此在进行 FPGA 芯片设计时,可利用这一特点按实现功能把整个模块分成多个子模块,然后在 VHDL 的顶层文件中调用这些模块,实现预期的功能。笔者把整个模块分为三个子模块,即系统计时模块、单通道记录模块以及 32 通道选通模块。以下具体阐述上述子模块及顶层模块的设计。

#### 1.2.1 系统计时模块

- (1) 实现功能 该模块用于提供 32 通道一个统一的时间刻度,并给单个通道记录模块提供声发射信号到达时间。

- (2) 设计方案 该模块为带复位输入和进位输出的 19 位同步计数器,复位输入用于整个芯片的复位,计数器满,即一次采样结束(采样时间长度为17.5ms)时将输出一个进位脉冲,用于复位 32 个单

通道记录模块,进行下一次采样。

#### 1.2.2 单通道记录模块

- (1) 实现功能 该模块在声发射信号越过参考 门限时,记录对应通道信号到达时间以及振铃计数, 同时产生信号有效标志位。

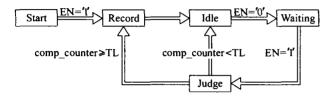

- (2) 设计方案 为提高工作速度以及电路的稳定性,可用同步方法来设计,由于记录过程的时序较复杂,可以利用 VHDL 状态机模型(图 2)来实现。以下对状态机中各状态进行简单描述:

图 2 记录模块的状态机模型示意图 comp\_counter——用于记录相邻两个脉冲时差的计数器

- (a) Start 在复位信号有效的情况下进入此状态。此时整个模块处于初始状态。

- (b) Record 当 EN='1'时,模块进入 Record 状态。该状态下,模块记录信号到达时间以及上一个信号的振铃计数值,并把标志位 flag 置'1',同时把 comp\_counter 清 0。

- (c) Idle Record 状态结束后,紧接着下一个时钟周期进入此状态。在 Idle 状态下,comp\_counter 开始计数。同时模块开始查询前面通道的flag 是否为'1',若是,则该通道把记录的数据保持住,flag 继续置'1'(通道 0 除外),直到前面的数据读取完(即 flag 为 0)才开始读取该通道的数据,读取完毕把该通道的 flag 清 0。

- (d) Waiting EN='0'时进入此状态。在Waiting 状态下, comp\_counter 继续计数,同时模块等待下一振铃脉冲的到来。

- (e) Judge 当下一个振铃脉冲出现(EN='1')时,电路进入此状态。在 Judge 状态下,模块立刻把内部 comp\_counter 计数器的当前值与 TL 进行比较。若 comp\_counter≥TL,则表示这是一个新的声发射信号,电路接下来进入 record 状态;反之若 comp\_counter<TL,则表示这个脉冲与前面一个脉冲是同一个声发射信号,zl\_counter 加 1,并且 comp\_counter 清 0,以用于进行下一次判断,电路进入 Idle 状态。

通过建立上述状态机模型,就可以完成单通道 记录模块的设计,该模块可以作为一个子模块,在顶 ·392 · 层文件中进行调用。

#### 1.2.3 32 通道选通模块

- (1) 实现功能 该模块用于协调 32 个单通道 记录模块,把记录的数据输出到芯片的输出端口,确 保不会产生数据丢失和总线竞争。

- (2)设计方案 由于每个通道都是并行工作的,因此有可能在某一时刻多个通道同时接收到声发射信号,这样对应模块就会立即记录下该信号的特征参数并输出,而整个芯片的外部输出端在某一时刻只能有一个通道的数据输出。因此在上述情况下就要考虑内部选通的问题。笔者的方案是,定义0通道优先级最高,然后从通道 $1,2,\cdots,31$ 依次递减。这样当第 $N(0 < N \le 31)$ 通道记录下参数,产生标志信号时,需要立即查询其前面的第 $N-1,N-2,\cdots,1,0$ 的每个通道的标志位是否为'1',如果是(表示前面的通道中有新数据并没有读走),则该第N通道的标志位一直处于置位状态(即把数据锁存起来),直到前面通道的标志位复位后才把该通道的数据读走。这样就可确保各通道的数据不丢失。

#### 1.2.4 顶层模块设计

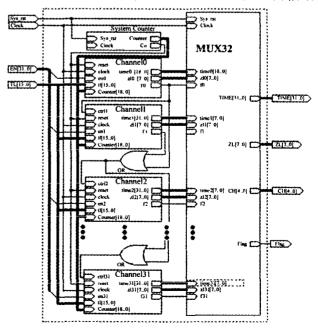

顶层模块的功能就是调用上述每个子模块,同时把子模块之间端口正确连接起来构成整个芯片的内部结构,实现预期的功能。顶层结构示于图 3。

#### 2 FPGA 综合、布局布线和时序仿真

#### 2.1 综合及布局布线

在用 VHDL 进行 FPGA 芯片设计后,需借助

图 3 FPGA 芯片的内部结构

EDA(电子设计自动化)工具进行综合,综合的目的就是把 VHDL语言转换为与 FPGA 结构相映射的 网表文件,然后再利用布局布线适配器调用网表文件进行优化和布局,生成 FPGA 配置文件,用于下载到具体的目标器件中。笔者使用的综合工具是 Synopsys 公司的 Fpga express,布局布线工具是 Altera 公司的 Max+PlusII, FPGA 芯片是 Altera 公司的 EP1K100QI208-2。

#### 2.2 时序仿真(功能验证)

在完成 FPGA 的综合和布局布线后,需进行时序仿真,目的是检验设计的结果与预期要求是否一致。时序仿真已将目标器件的硬件特性(如延时特性及建立保持时间等)考虑进去了,因此,仿真的结果与芯片的实际工作状况较吻合。

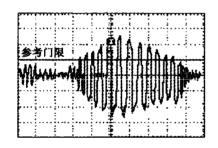

由于设计的 FPGA 芯片用于声发射检测中的特征参数提取,因此仿真时的输入信号应与实际声发射检测情况相符。为此,在时序仿真前,用铅笔芯断裂来模拟脉冲声发射源。然后通过设定某一参考门限来得到相应的振铃脉冲,图 4 和图 5 分别是用示波器观察到的断铅信号模拟的声发射信号波形和相应的振铃脉冲。

图 4 断铅信号模拟的声发射信号波形

图 5 设定参考门限产生的振铃脉冲(1μs/横格)

从图 5 可见,相邻振铃脉冲的最大间隔不到 10μs,而振铃脉冲本身的最大脉冲宽度为 5μs 左右。 在进行仿真时,输入信号将按上述要求进行设置。

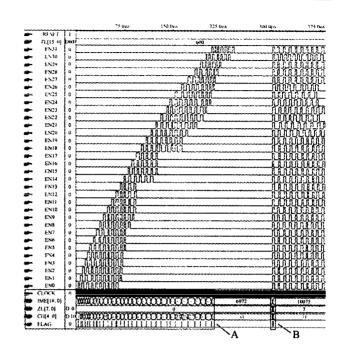

FPGA的时序仿真图示于图 6。图中,时钟频率为 30MHz,32 通道的输入脉冲信号(EN0~EN31)的脉冲宽度以及相邻两脉冲之间的间隔时间

图 6 32 通道声发射信号特征参数提取波形图

与图 5 中断铅信号模拟出来的声发射振铃脉冲类似。事件延时 TL 设定为 600 个时钟周期,相当于 20μs。整个时序仿真的时间为 400μs。

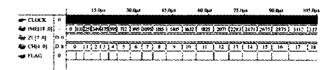

首先按先后顺序给每个通道(0~31)输入一串脉冲信号,相邻脉冲信号之间的间隔时间小于 TL值。从图 6 放大部分 A(图 7)可以看出,芯片将分别记录第一个脉冲信号的到达时间和对应通道号,同时产生一个时钟周期的高电平脉冲。

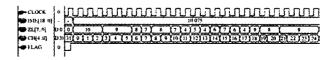

然后在某一时刻给 32 通道同时并行输入脉冲信号,该脉冲信号与其前面的脉冲信号间隔大于TL值。从图 6 放大部分 B(图 8)可以看出,芯片将按通道号由低到高的顺序,在每个时钟的上升沿依次记录下每个通道第一个脉冲到达时间和对应通道号以及上一次的振铃计数。由于是连续记录,因此输出的高电平脉冲为 32 个时钟周期。由此可见,系

图 7 32 通道顺序输入脉冲信号 系统提取特征参数波形图

图 8 32 通道并行输入脉冲信号系统提取特征参数波形图

## 第八届全国无损检测大会暨国际无损检测技术研讨会 电力系统第九届无损检测学术会议将于9月在苏州举行

由中国机械工程学会无损检测分会主办的第八届全国无损检测学术会议暨国际无损检测技术研讨会和展览会因"非典"延期,现定于 2003 年 9 月 23 ~26 日(9 月 22 日报到)在苏州国际会议展览中心举行。同时开展庆祝中国机械工程学会无损检测分会成立 25 周年活动。本次会议由苏州热工研究院有限公司(原国家电力公司苏州热工研究所)承办。届时中国电机工程学会火力发电分会的电力系统第九届无损检测学术会议将同期举行。会议录用论文 380 余篇,将正式出版。

欢迎国内外无损检测同仁及厂商企业踊跃参加 会议和展览会,交流新成果、新经验,研讨无损检测、 状态监测和寿命评估技术的应用现状和发展趋势, 促进无损检测事业的繁荣和创新。

有关事宜可与苏州热工研究院联系,地址:苏州市西环路 5号;邮编 215004;联系人:周在杞、刘金宏;手机:13962521408(周),13806219645(刘);电话: 0512-68602202, 68602412; 传真: 0512-68262502; E-mail: ndt@snpi. ac. cn; 网址: http://www.snpi. ac. cn/ndt/。 (大会组委会)

### 机械工业上海无损检测培训中心 2003 年下半年招生通知

机械工业无损检测人员培训中心今年下半年继续举办超声(UT),射线(RT),磁粉(MT),渗透(PT)和涡流(ET)Ⅱ级及Ⅰ级(初级)人员培训班。

今年采取滚动办学方法,以利于各单位自由选择学习时间。下半年具体办班日期:

UT班:7月12日~8月1日,9月1~19日,10月13~31日,11月10~30日。RT班:7月3~14日,12月8~19日。MT班:8月18~29日,11月3~14日。PT班:11月1~11日。ET班:8月4~11日,12月22~29日。

地点:上海市辉河路 100 号上海材料研究所内。 收费(培训、考试及证书资料费):UT,RT,ET 为 1 200 元/期: MT, PT 为 1 000 元/期。

资格证书:凡经培训及考试鉴定合格者,颁发与 德国无损检测学会互认的我国无损检测学会证书。

培训中心还可按企业及用户需要,接受合作培训及现场委托培训,欢迎联系接洽。

欲参加者请向培训中心报名,报名时请写明报 考者姓名、性别、年龄、学历和单位名称及所报考的 方法和级别,并写明所考方法的实践经历(年)。

联系地址:上海市辉河路 100 号,邮编:200437, 联系人:蔡美珍、桂根生,电话:(021)65556775× 412,482,传真:(021)55888795。

机械工业上海无损检测培训中心

#

统在 32 通道并行输入信号的极端情况下,记录所用时间为  $32/30=1.07\mu s$ ,而对于频率为几百千赫、周期为几微秒的声发射信号来说,在这种情况下,依然不会发生数据丢失,满足预期的目标要求。

#### 3 结论

通过 VHDL 语言设计 FPGA 芯片,实现了 32 通道声发射特征参数的提取,FPGA 在声发射检测 中的应用使得系统集成度大大提高、可靠性更高,同 时具有更强的实时性和良好的性价比,在多通道声 发射检测中源定位及其强度评价方面有着很好的应 用前景。

#### 参考文献:

- [1] 朱明程. FPGA 原理及应用设计 现场可编程逻辑门阵 列器件[M]. 北京:电子工业出版社,1994.

- [2] 赵雅兴. FPGA 原理、设计与应用[M]. 天津:天津大学 出版社,1999.

- [3] 侯伯亨,顾 新. VHDL 硬件描述语言与数字逻辑电路设计[M]. 修订版,西安:西安电子科技大学出版社, 1999.

- [4] 袁振明,马羽宽,何泽云. 声发射技术及其应用[M]. 北京: 机械工业出版社,1985.

- [5] Brown Stephen D, Vranesic Zvonko G. Fundamental of Digital Logic with VHDL Design [M]. Boston: McGraw-Hill, 2000.